DEMONSTRATORS

Demostrators will serve as pipe cleaners for our technologies

PREVAIL demonstrators have been chosen to showcase the technologies and applications that can be accessible via the project.

They are designed and fabricated using 300 mm and 200 mm wafer-size technology portfolios made available by the RTOs in PREVAIL.

The existing infrastructure of the RTOs supports the vast majority of the technology portfolios, while new tools procured via PREVAIL complement the technological capabilities of the new coordinated TEF.

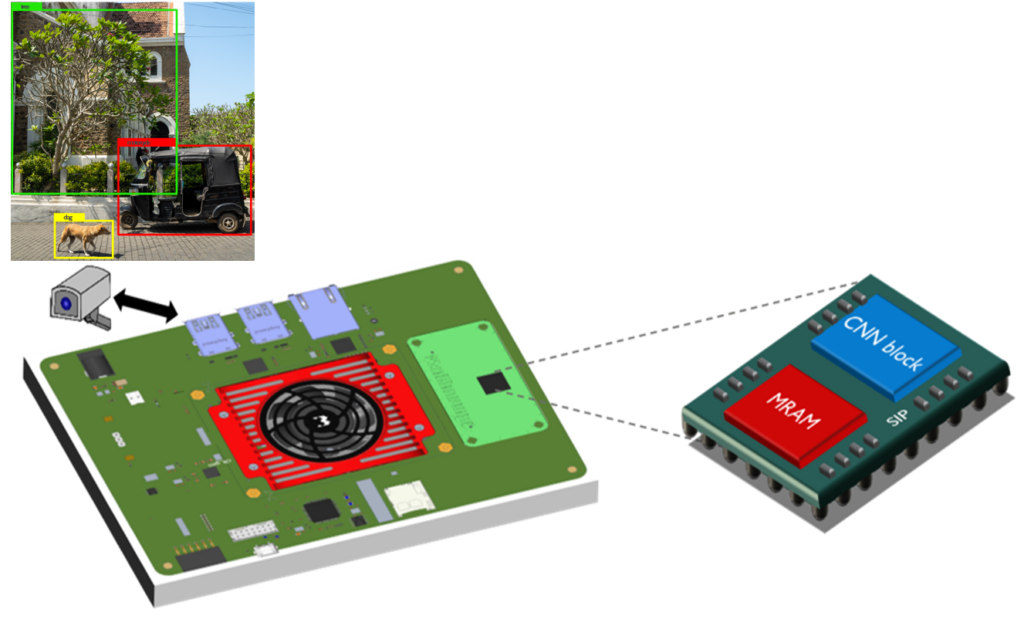

eNVM demonstrator

Current AI software solutions are primarily built on established hardware technologies and architectures that face limitations in reliability, precision, energy efficiency, and security.

New system architectures, such as the PREVAIL eNVM demonstrator, are being developed to address such limitations. This first demonstrator aims to showcase the application of NVM technology in edge AI scenarios such as image analysis and classification tasks.

Here, an AI-accelerator and a MRAM high-level cache memory will be connected through an FPGA platform to control the data acquisition and data flow. As a specific use-case, smart camera inputs will be analyzed with MRAM chips acting as video history buffer.

From the use-case definition to the assembling and testing, the design and manufacture of this demonstrator is shared among all the RTOs.

News about the evolution of this demonstrator will be announced in Q1/2026.

.

Combination of an AI-accelerator and a MRAM memory. System level view of PREVAIL’s demonstrator for image processing use-case.

Silicon Photonics demonstrator

Si-photonics technology can handle large volumes of real-time data and execute computing tasks quickly and efficiently. The proposed PREVAIL demonstrator aims to exemplify this application by leveraging the combined strengths of IMEC and LETI’s advanced photonics platforms to achieve best-in-class integration density, targeting a representative circuit for Artificial Intelligence applications.

IMEC’s active silicon photonics platform, combining high-quality active and passive components, is integrated with LETI’s backside evanescent coupling to enable heterogeneous integration or multi-level photonics circuits. This latter enablement is pursued through a photonic circuit that realizes a vector matrix product in the analogue domain while requiring low-loss silicon crossings.

The photonic circuit consists of three parts:

The resulting operation will lead to vector-matrix products performing at 10GHz+ rates.

.

Integrated photonics circuit – courtesy of imec.

This demonstrator is currently at design stage, updates on the status will be announced in Q1/2026.

3D-Integration demonstrator

The integration of heterogeneous components using 3D technologies is crucial for future system scaling, especially in high-performance, low-power systems where computing and memory functions are optimized and integrated.

This demonstrator addresses a real industrial problem with no current market solution: developing technologies that mix different interconnect methods. These include microbumps and hybrid bonding for die-to-wafer chiplet assembly, through silicon vias (TSVs) for through-wafer connectivity, backside redistribution layers (RDLs) and bump formation for package assembly, flip-chip connections, and packaging technologies for final assembly onto a substrate.

These building blocks enable new 3D technology flows for edge AI applications, leveraging the technological capabilities available through PREVAIL.

The Si-interposer-based technology proposed for this demonstrator targets the densest integration option, allowing for very high-density interconnect pitches and lines.

For the design, it has been necessary to use DRMs from three RTOs and 3D building blocks for fabrication on 300 mm wafers. Building this demonstrator requires starting three lots at different sites and then merging them into the final devices, testing the interoperability among the RTOs.

Schematic of 3D-integration demonstrator.

SIGN UP to receive first-hand news of the project and be part of the PREVAIL’s network.

For detailed technical enquiries regarding our offer, access and demonstrators go to CONTACT US.

PREVAIL project partners

PREVAIL

A multi-hub Test and Experimentation Facility for edge AI hardware

Grant Agreement No. 101083307